注意誤操作和扇出

在連接“標準邏輯IC”時,需要考慮一個輸出最大可連接的IC數量。

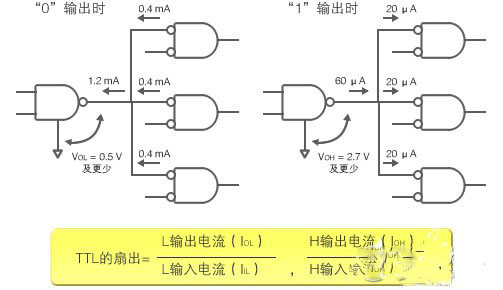

在TTL IC中,可連接IC的數量受到輸出電流的限制,我們把允許連接的IC上限個數稱為扇出。只要想起TTL IC是由雙極性晶體管構成的,就能容易地想象出開關切換時是需要電流的。TTL IC的扇出可以通過輸出電流除以輸入電流來求出(圖3)。需要注意的是如果連接的IC個數超過了扇出數,將無法保證輸出的邏輯電平。

圖3:TTL IC的扇出

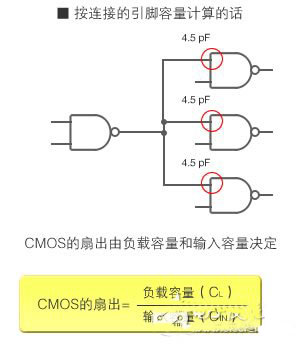

由于CMOS IC的輸入引腳中幾乎沒有電流,因此無法根據電流計算它的扇出數。需要根據負載容量計算(圖4)。

在CMOS IC的數據表中,通過傳播延遲時間的測量方法明確記載了負載容量。如超過負載容量,傳播延遲時間將變長,可能引起誤操作,需要注意。

圖4:CMOS IC的扇出

輸出線之間連接,漏極開路

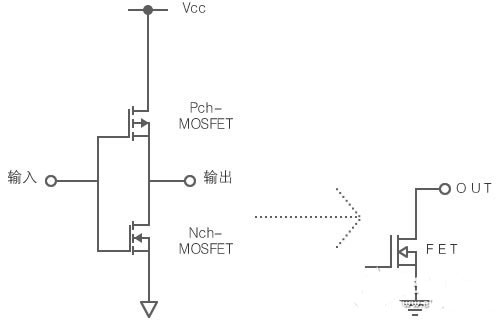

漏極開路是指不能輸出高電平(High)的FET(如圖A右圖)。在漏極開路的電路中,不存在通常CMOS IC輸出段(如圖A左圖)中和VCC相連的MOSFET,所以,無法輸出高電平。只能輸出Low或高阻抗(輸出端和電路是斷開的,是一個無法輸出電流和電壓的狀態)。

在高阻抗的情況下,由于輸出不穩定,因此需要通過電阻和電源相連,把輸出端固定在High電平下使用。該電阻稱為上拉電阻。

由于上拉電阻連接的電壓不需要與電源電壓相同,因此可以連接邏輯電平不同的IC。

圖A:CMOS輸出與漏極開路輸出

組合邏輯電路

邏輯電路中,只通過輸入信號的組合方式決定輸出的邏輯電路稱作“組合邏輯電路”。

相反,內部擁有記憶電路和同步電路,只通過輸入信號的組合無法決定輸出的邏輯電路被稱作“時序邏輯電路”。

本期只對前者“組合邏輯電路”進行講解。

“組合邏輯電路”是通過組合多個AND、OR、NOT、XOR等邏輯門而構成的。可以理解為用多個邏輯門的排列就能實現多種功能的電路。

首先讓我們來看看“組合邏輯電路”的代表元器件,多路復用器和解碼器。

可選擇輸出信號的多路復用器

多路復用器是可以從多個輸入信號中選擇一個輸出信號的信號切換器。可以通過自動售貨機來想象其工作模式。各種飲料的按鈕就是輸入信號,當按下選擇按鈕后,從同一出貨口可以拿到各種飲料。

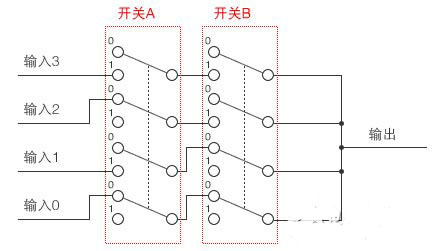

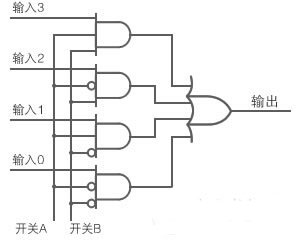

如果用開關說明多路復用器的工作原理,如圖5所示。開關A包括4個縱向聯動開關。開關B也是一樣。那么,當開關A為0,開關B也為0時,可以看到輸入0連接到輸出上,也就是輸入0的信號被輸出。同樣,當開關A為1,開關B為0時,輸入1的信號將連接到輸出上。當開關A為0,開關B為1時,輸出2的信號將連接到輸出上。當開關A為1,開關B為1時,輸入3的信號將連接到輸出上。也就是說,可以通過開關A和開關B從4個輸入中選擇一個輸出。這就是實現信號切換的多路復用器電路。

圖5:用開關構成的多路復用器

多路復用器用邏輯電路表示的話,就象圖6所示,只需要AND和OR就可以實現。AND部分進行判斷,OR部分用于選擇一個信號輸出。

圖6:用邏輯電路構成的多路復用器

判斷輸入的解碼器

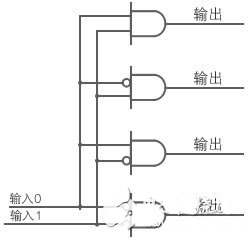

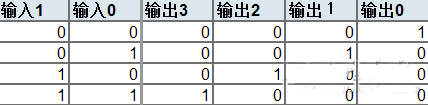

請看解碼器的真值表(圖8)。由該表可知, 2個輸入信號可通過4個輸出信號中的一個輸出。比如當兩個輸入為二進制時,讓4個輸出信號分別對應十進制的0、1、2、3,就可以認為這是一個將二進制解碼為十進制的電路。

圖7:用邏輯電路構成的解碼器

圖8:解碼器真值表

除此之外,還有比較器、加法器(全加器/半加器)、乘法器、減法器、桶形移位器等多種“組合邏輯電路”。其中大多數都是應用多路復用器和解碼器制作而成的。但是,如果只是應用而不做改善的話,將出現電路冗長等問題,所以,需要簡化并壓縮電路。